Hotline:0755-22277778

Teléfono: 0755 - 2227778

Teléfono móvil: 13826586185 (párrafo)

Fax: 0755 - 22277776

Correo electrónico: duanlian@xianjinyuan.cn

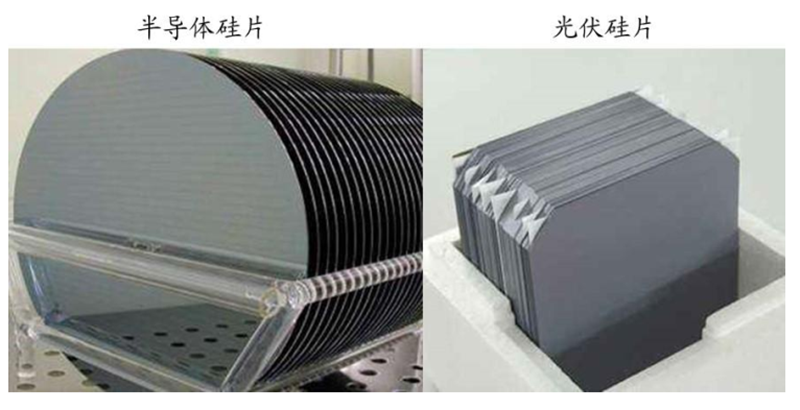

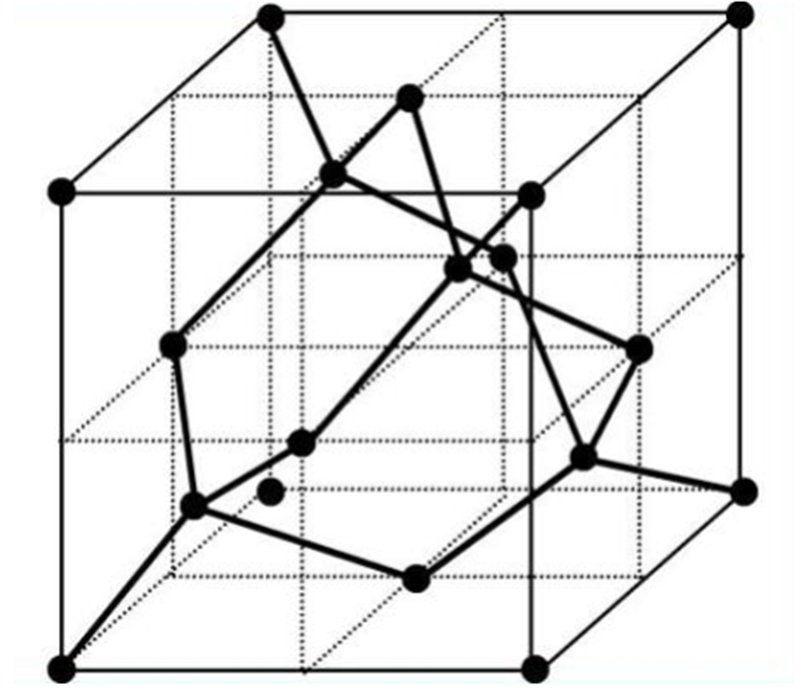

Los materiales de silicio se dividen en silicio monocristalino y polisilicio de acuerdo con la disposición de las células cristalinas. La mayor diferencia entre el silicio monocristalino y el polisilicio es que la fila celular del silicio monocristalino es ordenada, mientras que el polisilicio es desordenado. En términos de métodos de fabricación, el polisilicio generalmente se hace vertiendo el silicio directamente en el crisol para derretirlo y luego enfriarlo. El silicio monocristalino forma una barra de cristal (método de tracción directa) tirando de un cristal único. En términos de propiedades físicas, las propiedades de los dos tipos de silicio son muy diferentes. El silicio monocristalino tiene una fuerte capacidad de conducción eléctrica y una alta eficiencia de conversión fotoeléctrica. la eficiencia de conversión fotoeléctrica del silicio monocristalino es generalmente de alrededor del 17% al 25%, y la eficiencia del polisilicio es inferior al 15%.

▲ estructura celular de silicio monocristalino

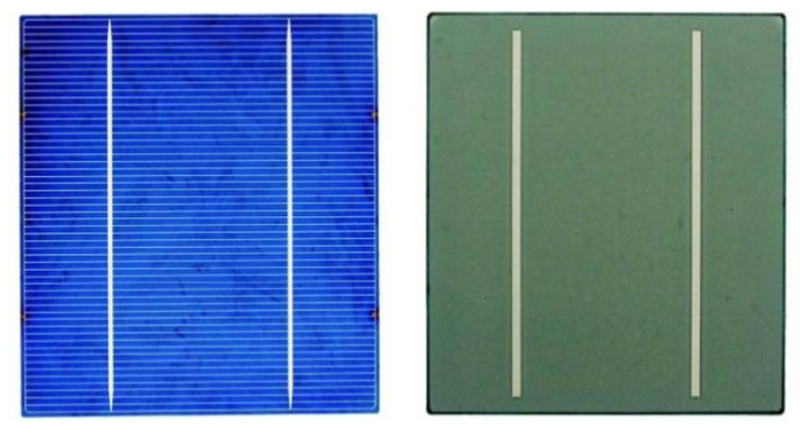

Silicio fotovoltaico: debido al efecto fotovoltaico y las ventajas obvias del silicio monocristalino, las personas utilizan silicio para completar la conversión de energía solar a eléctrica. Las láminas de silicio monocristalino generalmente redondeadas y cuadradas utilizadas en el campo fotovoltaico. También se utilizan láminas eléctricas de polisilicio más baratas, pero la eficiencia de conversión es baja.

▲ positivo y negativo de la batería de silicio monocristalino

▲ positivo y negativo de la placa de batería de polisilicio

Debido a los bajos requisitos de pureza, deformación y otros parámetros de las pastillas de silicio fotovoltaico, el proceso de fabricación es relativamente simple. Tomando como ejemplo las baterías de silicio monocristalino, el primer paso es cortar el círculo cuadrado, primero cortar la barra de silicio monocristalino en una barra cuadrada de acuerdo con los requisitos de tamaño, y luego redondear las cuatro esquinas de la barra cuadrada. El segundo paso es el lavado ácido, principalmente para eliminar las impurezas superficiales de las barras cuadradas monocristalinas. El tercer paso es cortar en rodajas, primero pegar la barra cuadrada limpia con la placa de trabajo. A continuación, coloque la placa de trabajo en la cortadora y Corte de acuerdo con los parámetros de proceso ya establecidos. Finalmente, las láminas de silicio monocristalino se limpian para monitorear la suavidad de la superficie, la resistencia y otros parámetros.

Pastillas de silicio semiconductoras: las pastillas de silicio semiconductoras son más exigentes que las pastillas de silicio fotovoltaico. En primer lugar, todas las pastillas de silicio utilizadas en la industria de semiconductores son monocristalinas, con el objetivo de garantizar las mismas características eléctricas de cada bit de pastillas de silicio. En términos de forma y tamaño, las láminas de silicio monocristalino para fotovoltaica son cuadradas y tienen principalmente tipos de 125 mm, 150 mm y 156 mm de largo lateral. Por su parte, las pastillas de silicio monocristalino para semiconductores son redondas, con un diámetro de 150 mm (obleas de 6 pulgadas), 200 mm (obleas de 8 pulgadas) y 300 mm (obleas de 12 pulgadas). En cuanto a la pureza, las pastillas de silicio monocristalino para fotovoltaica requieren un contenido de silicio entre 4n - 6n (99,99% - 999999%), pero las pastillas de silicio monocristalino para semiconductores son de alrededor de 9n (9999999999% - 11n% (9999999999%), y el requisito de pureza es de al menos 1000 veces mayor que las pastillas de silicio monocristalino para fotovoltaica. En términos de apariencia, la planitud, suavidad y limpieza de las pastillas de silicio para semiconductores en la superficie son más exigentes que las pastillas de silicio fotovoltaicas. La pureza es la mayor diferencia entre las pastillas de silicio monocristalino para fotovoltaica y las pastillas de silicio monocristalino para semiconductores.

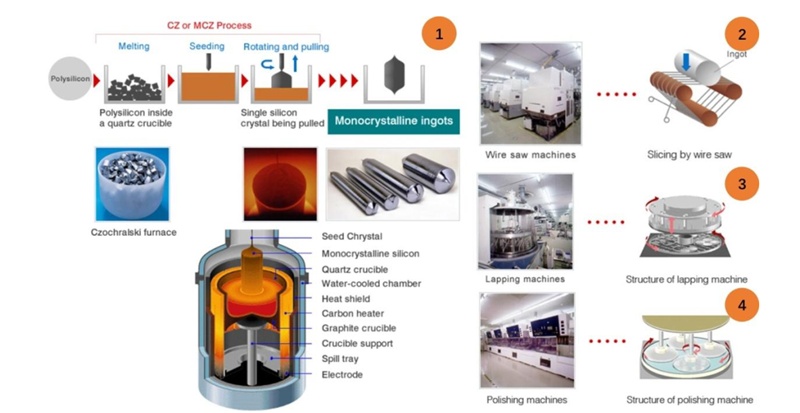

▲ proceso de fabricación de pastillas de silicio semiconductoras

El desarrollo de la Ley de Moore es el desarrollo de las pastillas de silicio. Debido a que las pastillas de silicio para semiconductores son redondas, las pastillas de silicio para semiconductores también se llaman "obleas de silicio" o "obleas". Las obleas son el "sustrato" para la fabricación de chips, y todos los chips se fabrican en este "sustrato". En el proceso de desarrollo de las pastillas de silicio para semiconductores, hay dos direcciones principales: tamaño y estructura.

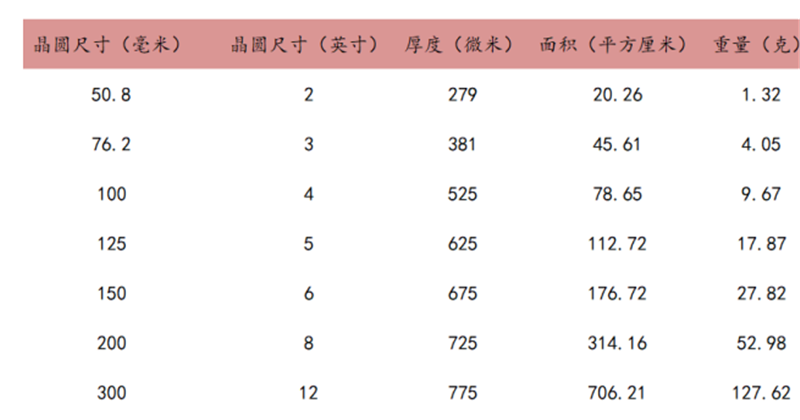

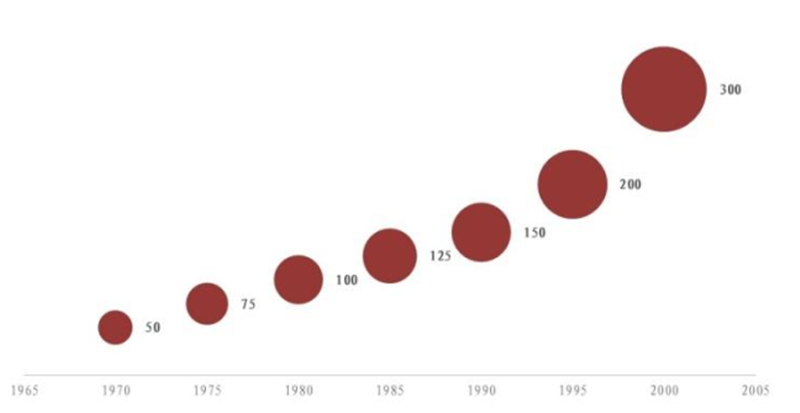

En términos de tamaño, el camino de desarrollo de las pastillas de silicio es cada vez mayor: en los primeros días del desarrollo de los circuitos integrados, se utilizaron obleas de 0,75 pulgadas. Aumentar el área de la obleas y aumentar el número de chips en una sola obleas puede reducir los costos. Alrededor de 1965, con la propuesta de la Ley de moore, la tecnología de circuitos integrados y las pastillas de silicio marcaron el comienzo de un período de rápido desarrollo. Las pastillas de silicio han pasado por nodos de 4, 6, 8 y 12 pulgadas. Desde que Intel e IBM desarrollaron conjuntamente la fabricación de chips de obleas de 12 pulgadas en 2001, las pastillas de silicio convencionales son ahora obleas de 12 pulgadas, lo que representa alrededor del 70%, pero las obleas de 18 pulgadas (450 mm) están en la agenda.

▲ parámetros de obleas de diferentes tamaños

▲ desarrollo del tamaño de las pastillas de silicio

En términos estructurales, la dirección de desarrollo de las pastillas de silicio es cada vez más compleja: en los primeros días del desarrollo de los circuitos integrados, solo había chips lógicos, pero con el aumento de los escenarios de aplicación, aparecieron chips lógicos, dispositivos de potencia, chips analógicos, chips mixtos digitales y analógicos, chips de memoria flash / dram, chips de radiofrecuencia, etc., lo que hizo que las pastillas de silicio aparecieran en diferentes formas estructurales. Ahora, hay tres tipos principales:

PW(Polish Wafer): Láminas pulidas. Debido a que las pastillas de silicio obtenidas por el corte directo después de tirar del cristal único no son perfectas en términos de suavidad o deformación, primero deben ser pulidas. Esta forma también es la forma más original de procesar las pastillas de silicio.

AW(Anneal Wafer): Obleas recolocadas. Con el desarrollo continuo de la tecnología de proceso, el tamaño característico del Transistor se reduce constantemente, y las deficiencias de las hojas pulidas se exponen gradualmente, como los defectos locales de celosía en la superficie de las pastillas de silicio y el alto contenido de oxígeno en la superficie de las pastillas de silicio. Para resolver estos problemas, se ha desarrollado la tecnología de obleas de recocido. Después del pulido, las pastillas de silicio se colocan en un tubo de horno lleno de gas inerte (generalmente argón) y se recolocan a alta temperatura. Esto no solo puede reparar los defectos de la red cristalina en la superficie de las pastillas de silicio, sino también reducir el contenido de oxígeno en la superficie.

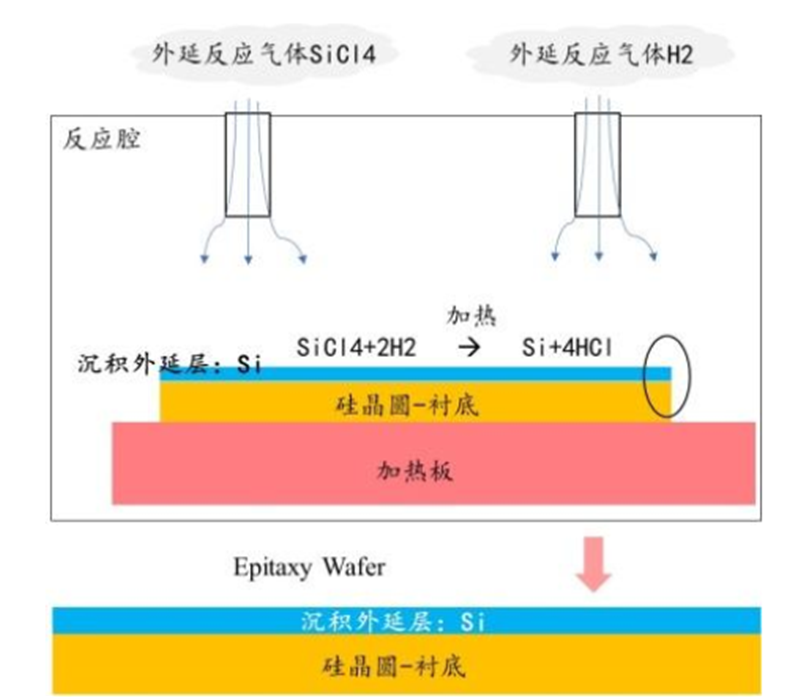

EW(Epitaxy Wafer): Silicio de capa epitaxial. A medida que aumentan los escenarios de aplicación de los circuitos integrados, las pastillas de silicio estándar fabricadas por las fábricas de pastillas de silicio ya no pueden cumplir con los requisitos de algunos productos en términos de características eléctricas. Al mismo tiempo, los defectos de celosía reducidos a través del recocido térmico no pueden satisfacer las necesidades de ancho de línea cada vez más pequeñas. Esto derivó en pastillas de silicio de capa epitaxial. La capa epitaxial habitual es la película de silicio. Es sobre la base de las pastillas de silicio originales, utilizando la tecnología de depósito de película delgada para cultivar una película de silicio. Debido a que en la extensión externa del silicio, el sustrato de silicio existe como modo de cristal de semilla, el crecimiento de la capa epitaxial replicará la estructura cristalina de la silicio. Debido a que las pastillas de silicio del sustrato son monocristalinas, la capa epitaxial también es monocristalina. Sin embargo, debido a que no se ha pulido, los defectos de celosía en la superficie de la pastilla de silicio después del crecimiento pueden reducirse a un nivel muy bajo.

Los indicadores técnicos de Epitaxia incluyen principalmente el espesor de la capa epitaxial y su uniformidad, la uniformidad de la resistencia eléctrica, el control del metal a granel, el control de partículas, el error de capa, la dislocación y otros controles de defectos. En esta etapa, se ha logrado una alta calidad de silicio de capa epitaxial optimizando la temperatura de reacción de la epitaxia, la velocidad de flujo del gas epitaxial, los gradientes de temperatura en el Centro y el borde. Debido a las diferentes necesidades de productos y actualizaciones tecnológicas, al optimizar constantemente el proceso de epitaxia, ahora se ha logrado una alta calidad de silicio epitaxial.

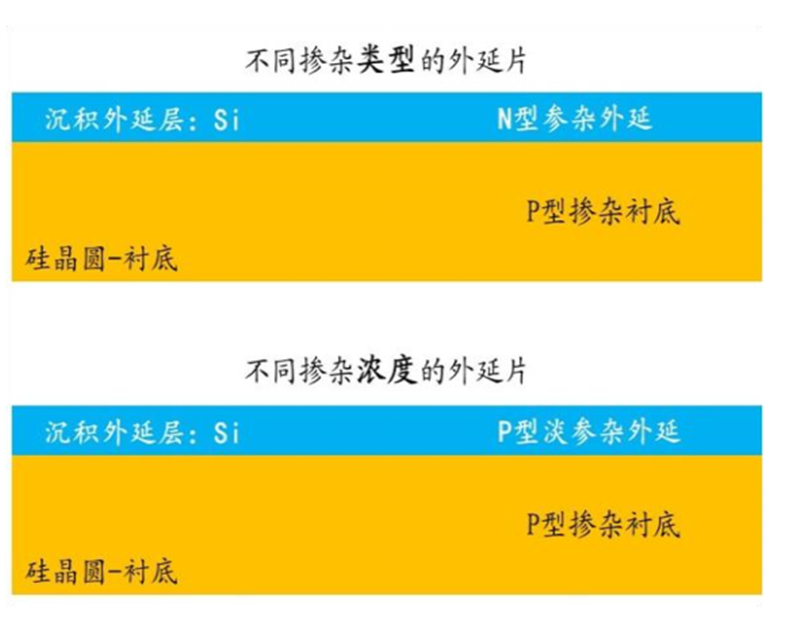

Además, ahora la tecnología ya puede generar capas epitaxiales con elementos dopados por resistencias eléctricas y concentraciones de dopaje diferentes de las pastillas de silicio originales, lo que facilita el control de las propiedades eléctricas de las pastillas de silicio cultivadas. Por ejemplo, se puede generar una capa de Epitaxia de silicio de tipo n en una silicio de tipo p, formando así una Unión PN mixta de baja concentración, optimizando el voltaje de ruptura y reduciendo el efecto de pestillo en la fabricación posterior de chips. El espesor de la capa epitaxial generalmente varía según el escenario de uso. en general, el espesor del chip lógico es de aproximadamente 0,5 micras a 5 micras. debido a que el dispositivo de potencia necesita soportar un alto voltaje, el espesor es de aproximadamente 50 micras a 100 micras.

▲ proceso de crecimiento de las pastillas de silicio epitaxiales

▲ las diferentes misceláneas de las películas de extensión

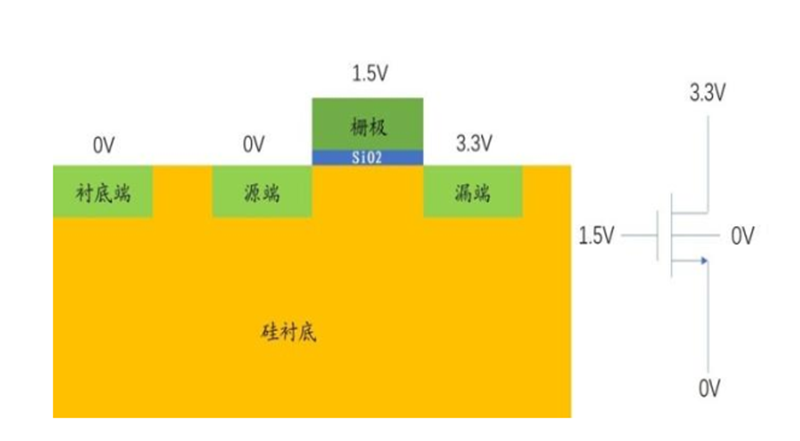

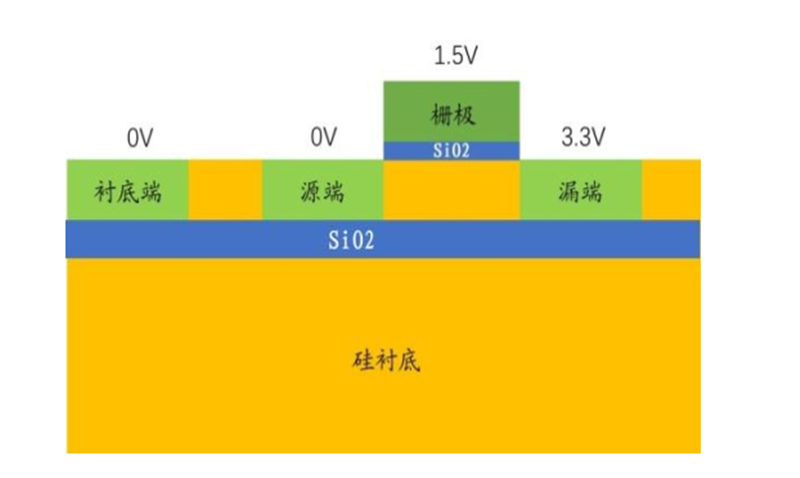

SW (soi wafer): el nombre completo de soi es Silicon - on - insulator (silicio sobre aislador). Debido a que las pastillas de silicio soi tienen las ventajas de pequeña capacidad parasitaria, pequeño efecto de canal corto, alta densidad de herencia, alta velocidad y bajo consumo de energía, especialmente en el bajo ruido del sustrato, las pastillas de silicio soi a menudo se utilizan en chips Front - end de radiofrecuencia.

▲ estructura mos de silicio ordinario

▲ estructura mos de silicio soi

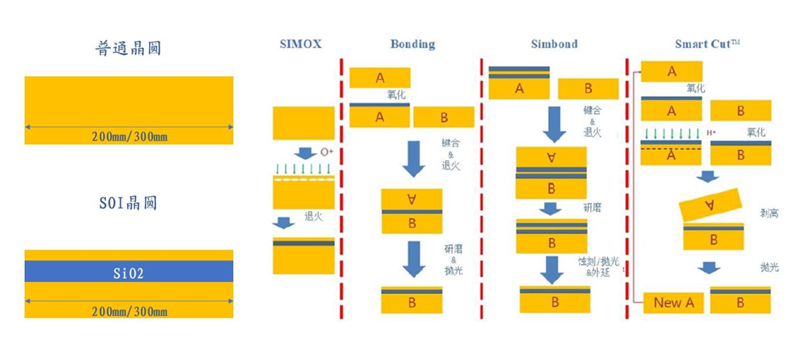

Hay cuatro métodos principales para fabricar pastillas de silicio soi: la tecnología simox, la tecnología bonding, la tecnología SIM - Bond y la tecnología SMART - cuttm; El principio de las pastillas de silicio soi es relativamente simple, y el objetivo central es agregar una capa aislante en el medio del sustrato (generalmente sio2 es el principal).

▲ cuatro tecnologías para la fabricación de pastillas de silicio soi

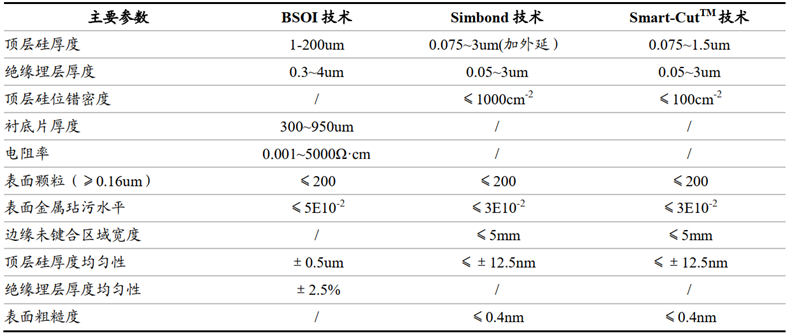

Desde el punto de vista de los parámetros de rendimiento, la tecnología SMART - cuttm es la mejor tecnología de fabricación de silicio soi en la actualidad. El rendimiento de la tecnología simpond no es muy diferente del rendimiento de la tecnología SMART - cut, pero en términos de espesor de silicio de alto nivel, las pastillas de silicio soi producidas por la tecnología SMART - cut son más delgadas, y en términos de costos de producción, la tecnología SMART - cut puede reutilizar las pastillas de silicio. para futuras producciones En masa, la tecnología SMART - cut tiene una ventaja de costo, por lo que ahora la industria reconoce que la tecnología SMART - cut es la dirección de desarrollo de las pastillas de silicio soi en el futuro.

▲ comparación de rendimiento de diferentes tecnologías de fabricación de pastillas de silicio soi

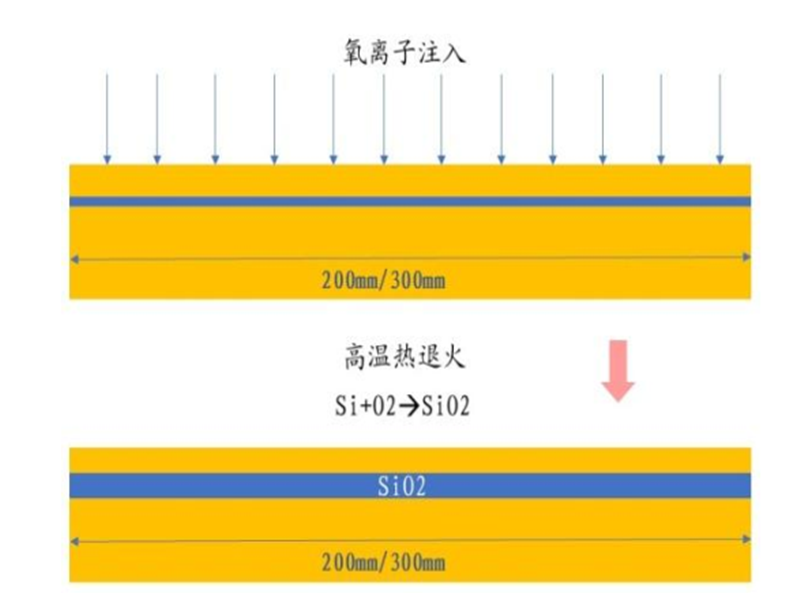

Tecnología simox: el nombre completo de simox es Separation by replanteed Oxygen (tecnología de aislamiento por inyección de oxígeno). Los átomos de oxígeno se inyectan en la obleas y luego se recolocan a alta temperatura para que los átomos de oxígeno reaccionen con los átomos de silicio circundantes para producir una capa de sílice. La dificultad de esta tecnología es controlar la profundidad y el espesor de la implantación de iones de oxígeno. Los requisitos técnicos para la implantación de iones son altos.

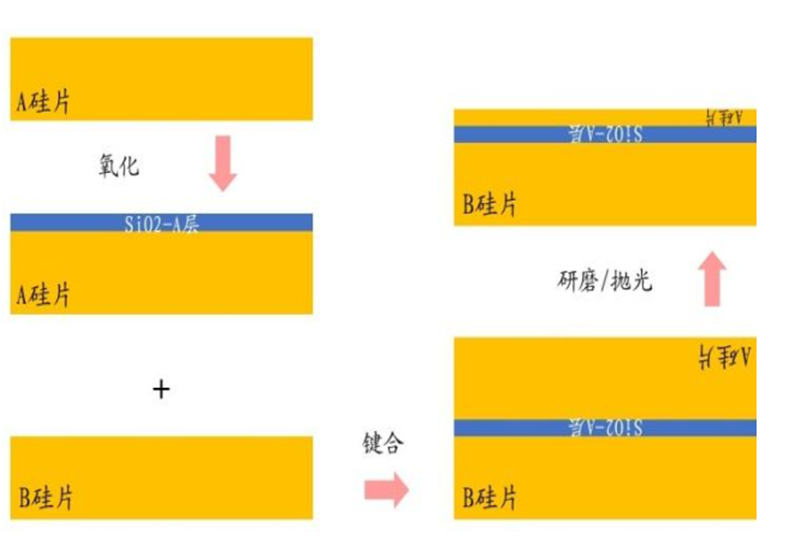

Tecnología de bonding: la tecnología de Bonding también se llama tecnología de unión, y las pastillas de silicio soi fabricadas con Bonding también se llaman Bonded soi, conocidas como bsoi. La tecnología Bonding requiere dos obleas de silicio ordinarias, en las que se crece una capa de óxido (sio2) y luego se une a otra fuente de silicio, y la Unión es la capa de óxido. Finalmente, se muele y Pule a la profundidad deseada de la capa de vertedero (sio2). Debido a que la tecnología de unión es más simple que la tecnología de implantación de iones, la mayoría de las pastillas de silicio soi se fabrican actualmente con tecnología de unión.

▲ el método de implantación de iones forma silicio sobre aislador

▲ el método wafer Bonding forma silicio sobre aislador

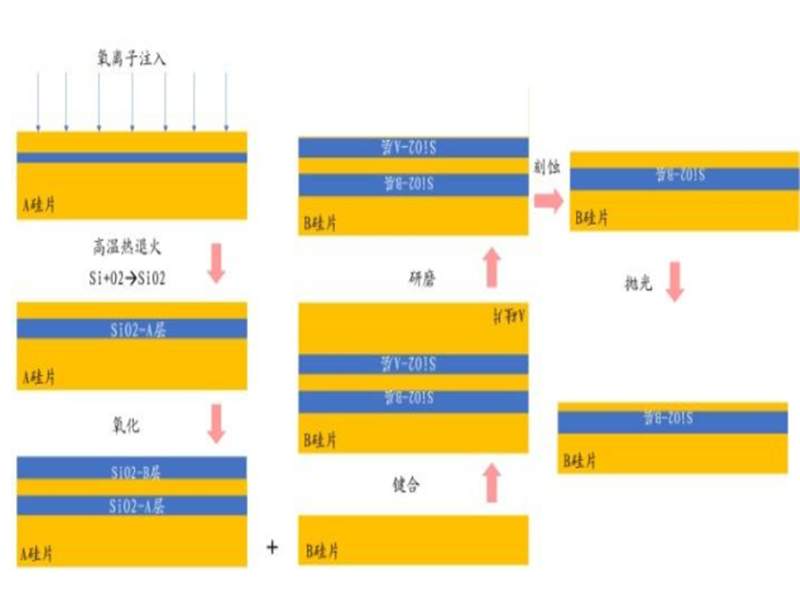

Tecnología SIM - bond: tecnología de unión por inyección de oxígeno. La tecnología SIM - Bond es una combinación de simox y la tecnología bond. La ventaja es que el espesor de la capa de oxígeno enterrada se puede controlar con alta precisión. El primer paso es inyectar iones de oxígeno en una hostia de silicio, luego recolocarla a alta temperatura para formar una capa de óxido, y luego formar una capa de óxido de sio2 en la superficie de la hostia de silicio. El segundo paso es unir la pastilla de silicio a otra pastilla. Luego, el recocido a alta temperatura forma una interfaz de unión intacta. El tercer paso es el proceso de adelgazamiento. Se utiliza la tecnología CMP para adelgazar, pero a diferencia de la tecnología bonds, SIM - Bonds tiene una capa de parada automática que se detiene automáticamente cuando se muele a la capa sio2. Luego, la capa de sio2 fue eliminada por corrosión. El último paso es pulir.

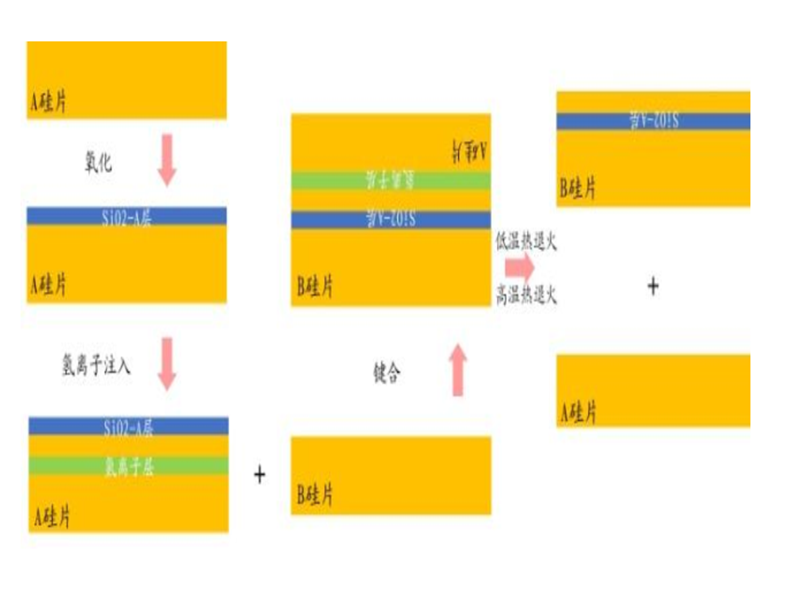

Tecnología SMART - cut: tecnología de desprendimiento inteligente. La tecnología SMART - cut es una extensión de la tecnología de unión. El primer paso es oxidar una hostia y generar sio2 de espesor fijo en la superficie de la hostia. El segundo paso es utilizar la tecnología de implantación de iones para inyectar iones de hidrógeno en la profundidad fija de la obleas. El tercer paso es unir otra obleas con obleas oxidadas. El cuarto paso es utilizar la tecnología de recocido térmico a baja temperatura, los iones de hidrógeno forman burbujas de aire, haciendo que una parte de la silicio se desprenda. Luego, se utiliza la tecnología de recocido térmico de alta temperatura para aumentar la resistencia a la unión. El quinto paso es aplanar la superficie del silicio. Esta tecnología es la dirección de desarrollo de la tecnología SOI reconocida internacionalmente, y el espesor de la capa de oxígeno enterrada está completamente determinado por la profundidad de la implantación de iones de hidrógeno, que es más precisa. Y las obleas desprendidas se pueden reutilizar, lo que reduce considerablemente los costos.

▲ el método SIM - Bond forma silicio sobre aislador

▲ el método SMART - cut forma silicio sobre aislador

Academia avanzada (shenzhen) Technology co., Ltd., © 2021www.avanzado.cn. todos los derechos reservados © 2021www.xianjinyuan.cn. todos los derechos reservados