Hotline:0755-22277778

Tel:0755-22277778

Mobile:13826586185(Mr.Duan)

Fax:0755-22277776

E-mail:duanlian@xianjinyuan.cn

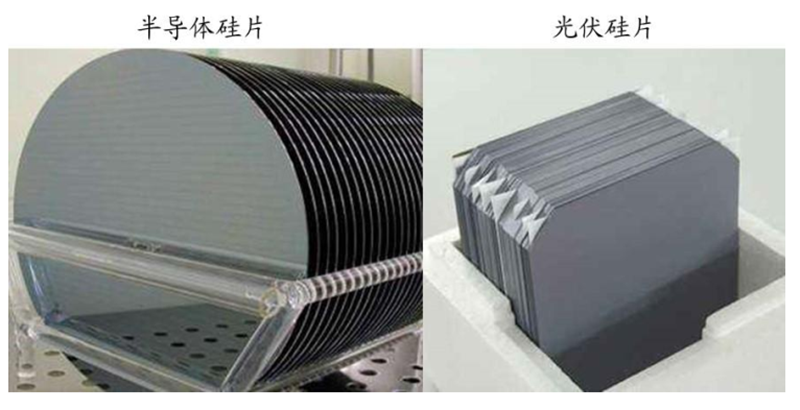

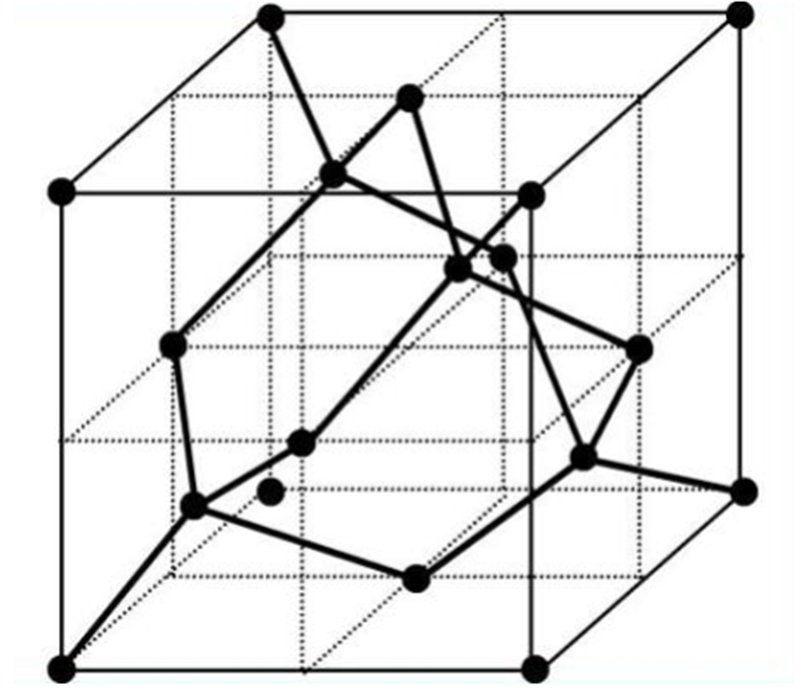

Silicon materials are divided into monocrystalline silicon and polycrystalline silicon based on the arrangement of their unit cells. The biggest difference between monocrystalline silicon and polycrystalline silicon is that the cell arrangement of monocrystalline silicon is ordered, while polycrystalline silicon is disordered. In terms of manufacturing methods, polycrystalline silicon is generally melted by directly pouring silicon material into a crucible, and then cooled. Monocrystalline silicon is formed into crystal rods by pulling single crystals (direct pulling method). In terms of physical properties, there is a significant difference in the characteristics between the two types of silicon. Monocrystalline silicon has strong conductivity and high photoelectric conversion efficiency. The photoelectric conversion efficiency of monocrystalline silicon is generally around 17% to 25%, while that of polycrystalline silicon is below 15%.

▲ Single crystal silicon cell structure

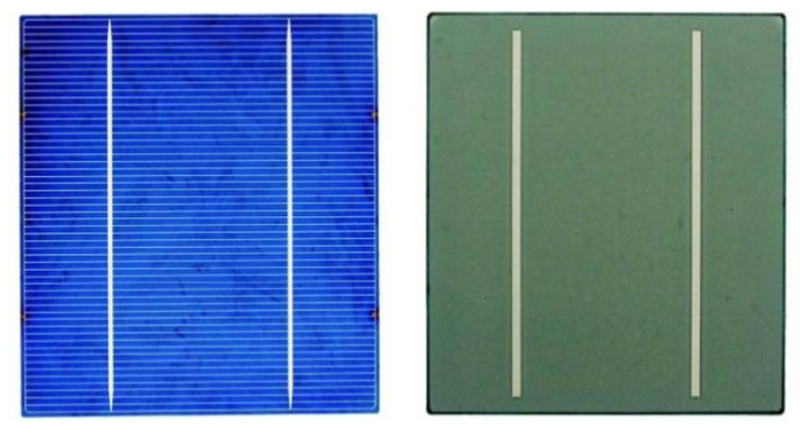

Photovoltaic silicon wafer: Due to the photoelectric effect and the obvious advantages of single crystal silicon, people use silicon wafers to convert solar energy into electrical energy. The commonly used monocrystalline silicon solar cells in the photovoltaic field are rounded square shaped cells. Cheaper polycrystalline silicon wafers are also used, but with lower conversion efficiency.

▲ Front and back of monocrystalline silicon solar cells

▲ Front and back of polycrystalline silicon solar cells

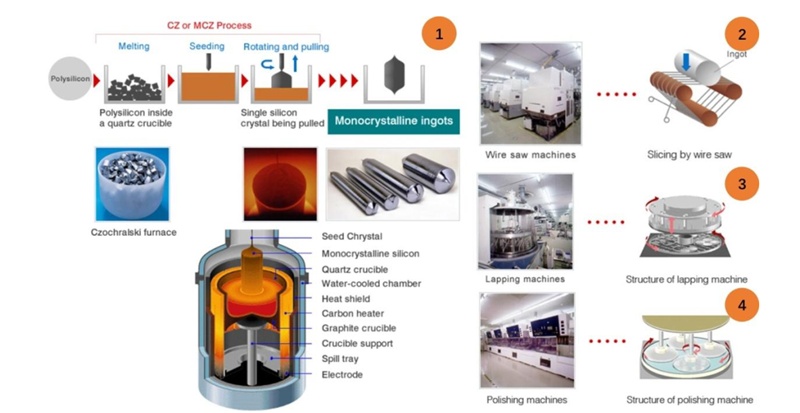

Due to the low requirements for purity, curvature, and other parameters of photovoltaic silicon wafers, the manufacturing process is relatively simple. Taking monocrystalline silicon solar cells as an example, the first step is to cut the monocrystalline silicon rod into square bars according to the size requirements, and then round the four corners of the square bars. The second step is acid washing, mainly to remove surface impurities from the single crystal square rod. The third step is slicing, first paste the cleaned square rod with the work board. Then place the work board on the slicer and cut it according to the pre-set process parameters. Finally, clean the monocrystalline silicon wafer and monitor its surface smoothness, resistivity, and other parameters.

Semiconductor silicon wafers: Semiconductor silicon wafers have higher requirements than photovoltaic silicon wafers. Firstly, all silicon wafers used in the semiconductor industry are monocrystalline silicon, with the aim of ensuring the same electrical characteristics for each bit of the wafer. In terms of shape and size, monocrystalline silicon wafers for photovoltaics are square, mainly in the types of 125mm, 150mm, and 156mm side lengths. The monocrystalline silicon wafers used in semiconductors are circular, with silicon wafer diameters of 150mm (6-inch wafers), 200mm (8-inch wafers), and 300mm (12 inch wafers). In terms of purity, the purity requirement for monocrystalline silicon wafers used in photovoltaics is a silicon content between 4N-6N (99.99% -99.9999%), but for semiconductor monocrystalline silicon wafers, it is around 9N (99.99999999%) -11N (99.99999999%), with a minimum purity requirement of 1000 times that of monocrystalline silicon wafers used in photovoltaics. In terms of appearance, semiconductor silicon wafers have higher requirements for surface flatness, smoothness, and cleanliness than photovoltaic silicon wafers. Purity is the biggest difference between monocrystalline silicon wafers for photovoltaics and semiconductors.

▲ Manufacturing process of semiconductor silicon wafers

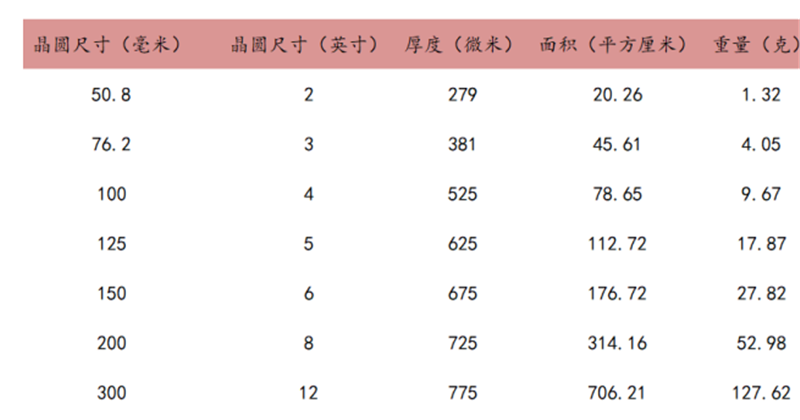

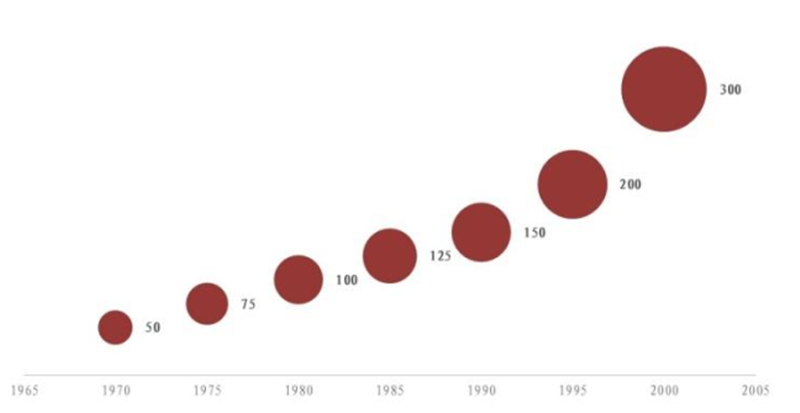

The development of Moore's Law is the development of silicon wafers. Due to the circular shape of silicon wafers used in semiconductors, they are also called "silicon wafers" or "wafers". The wafer is the "substrate" for chip manufacturing, and all chips are manufactured on this "substrate". In the development process of semiconductor silicon wafers, there are mainly two directions: size and structure.

In terms of size, the development path of silicon wafers is becoming increasingly larger: in the early stages of integrated circuit development, 0.75-inch wafers were used. Increasing the wafer area and increasing the number of chips on a single wafer can reduce costs. Around 1965, with the introduction of Moore's Law, both integrated circuit technology and silicon wafers entered a period of rapid development. Silicon wafers have gone through nodes such as 4-inch, 6-inch, 8-inch, and 12 inch. Since the joint development of 12 inch wafer chip manufacturing by Intel and IBM in 2001, the mainstream silicon wafer is now 12 inch wafers, accounting for about 70%, but 18 inch (450mm) wafers have been put on the agenda.

▲ Parameters of wafers of different sizes

▲ Development of silicon wafer size

In terms of structure, the development direction of silicon wafers is becoming increasingly complex: in the early stages of integrated circuit development, there was only one type, logic chips. However, with the increasing number of application scenarios, logic chips, power devices, analog chips, mixed signal chips, flash/DRAM storage chips, RF chips, and so on have emerged successively, resulting in different forms of silicon wafers in structure. Now, there are mainly three types:

PW(Polish Wafer): Polishing pads. The silicon wafer directly cut after pulling the single crystal is not perfect in terms of smoothness or curvature, so it needs to be polished first. This method is also the most primitive way of processing silicon wafers.

AW(Anneal Wafer): Annealing wafers. With the continuous development of process technology and the continuous reduction of transistor feature size, the disadvantages of polished wafers have gradually been exposed, such as local lattice defects on the surface of silicon wafers and high oxygen content on the surface of silicon wafers. To address these issues, annealing wafer technology has been developed. After polishing, place the silicon wafer in a furnace tube filled with inert gas (usually argon) for high-temperature annealing. This can not only repair the lattice defects on the surface of silicon wafers, but also reduce the surface oxygen content.

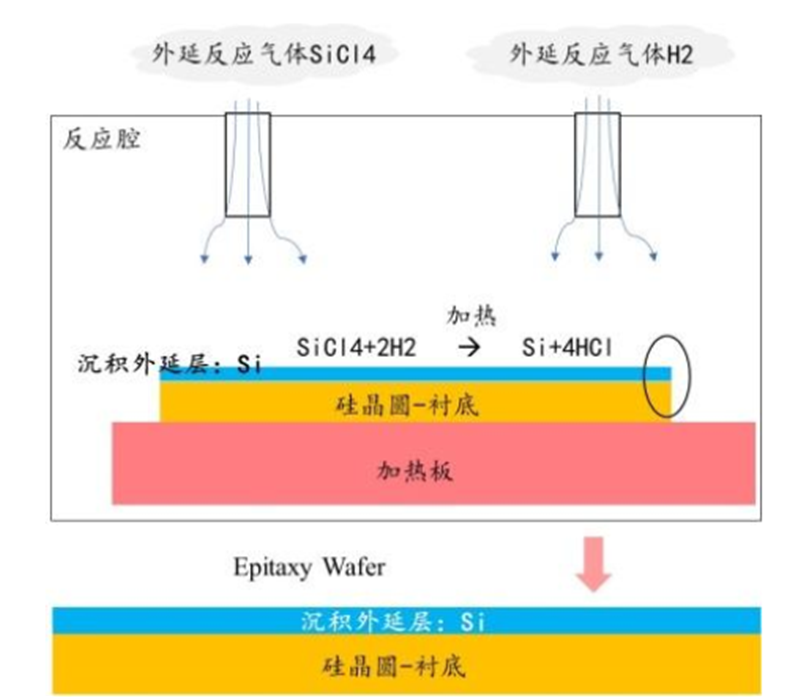

EW(Epitaxy Wafer): Epitaxial silicon wafer. With the increasing application scenarios of integrated circuits, standard silicon wafers manufactured by silicon wafer factories can no longer meet the electrical requirements of certain products. Meanwhile, the lattice defects reduced by thermal annealing cannot meet the increasingly smaller linewidth requirements. This gave rise to epitaxial silicon wafers. The usual epitaxial layer is a silicon thin film. It is based on the original silicon wafer and uses thin film deposition technology to grow a layer of silicon thin film. Due to the fact that the silicon substrate exists as a seed crystal in silicon epitaxy, growing epitaxial layers will replicate the crystal structure of the silicon wafer. Since the substrate silicon wafer is a single crystal, the epitaxial layer is also a single crystal. However, due to not being polished, the lattice defects on the surface of the grown silicon wafer can be reduced to a very low level.

The main indicators of epitaxial technology include epitaxial layer thickness and uniformity, resistivity uniformity, bulk metal control, particle control, layer faults, dislocations and other defect control. At present, people have achieved high quality epitaxial silicon wafers by optimizing the reaction temperature, flow rate of epitaxial gas, and temperature gradients at the center and edges. Due to different products and the need for technological upgrades, high quality epitaxial silicon wafers have been achieved through continuous optimization of epitaxial processes.

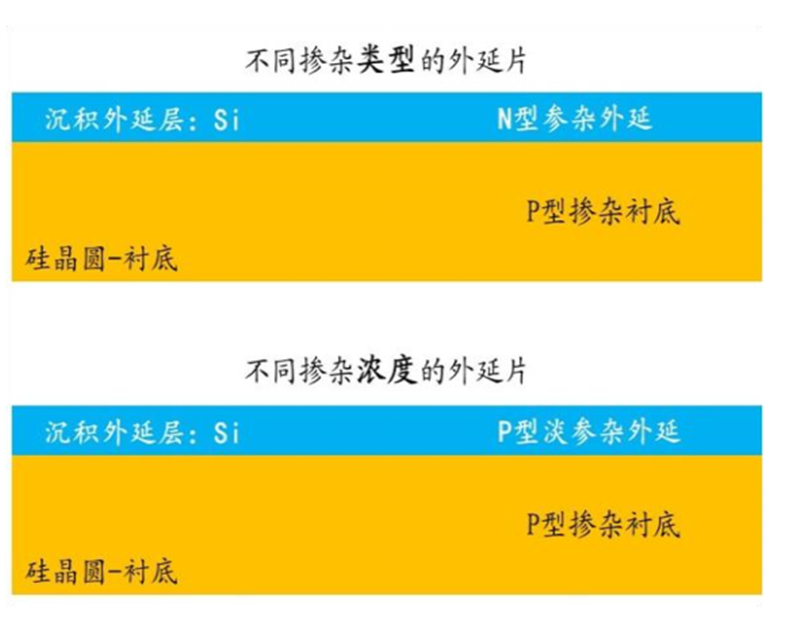

In addition, technology can now generate epitaxial layers with different resistivity doping elements and doping concentrations from the original silicon wafer, making it easier to control the electrical properties of the grown silicon wafer. For example, by generating an N-type silicon epitaxial layer on a P-type silicon wafer, a low concentration doped PN junction can be formed, which can optimize the breakdown voltage and reduce the latch up effect in subsequent chip manufacturing. The thickness of the epitaxial layer generally varies depending on the usage scenario. Generally, the thickness of logic chips is around 0.5 microns to 5 microns, while power devices need to withstand high voltages, so the thickness is around 50 microns to 100 microns.

▲ Epitaxial silicon wafer growth process

▲ Different doping of epitaxial wafers

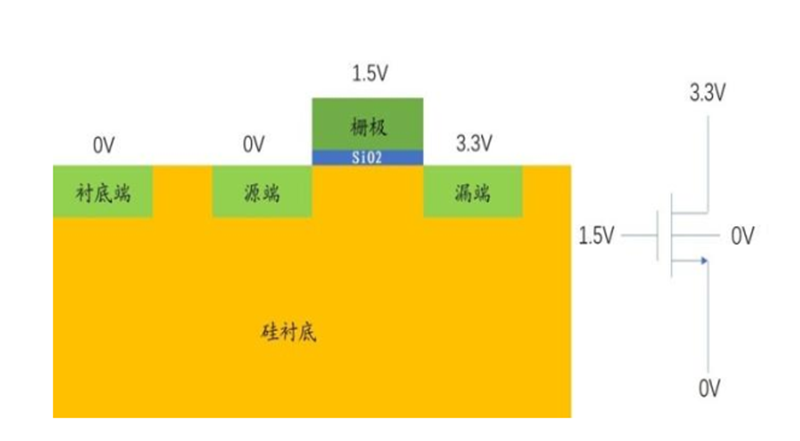

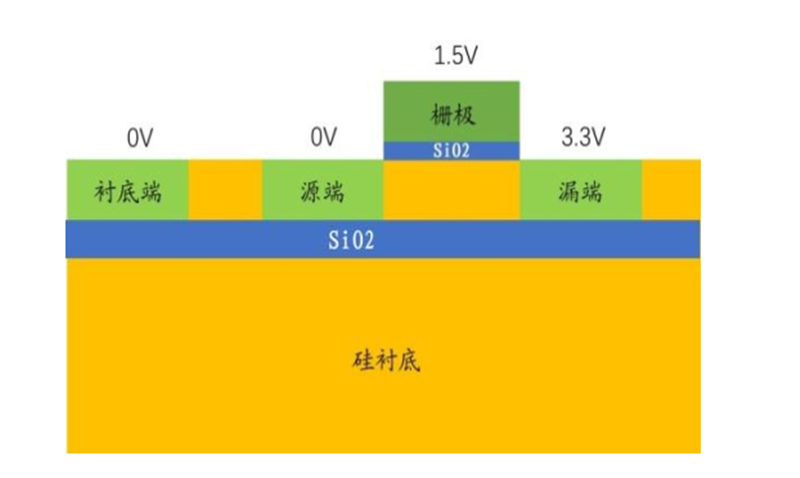

SW (SOI Wafer): SOI stands for Silicon On Insulator. Due to the advantages of low parasitic capacitance, short channel effect, high inheritance density, fast speed, and low power consumption of SOI silicon wafers, especially in terms of low substrate noise, SOI silicon wafers are often used in RF front-end chips.

▲ Ordinary silicon wafer MOS structure

▲ SOI silicon wafer MOS structure

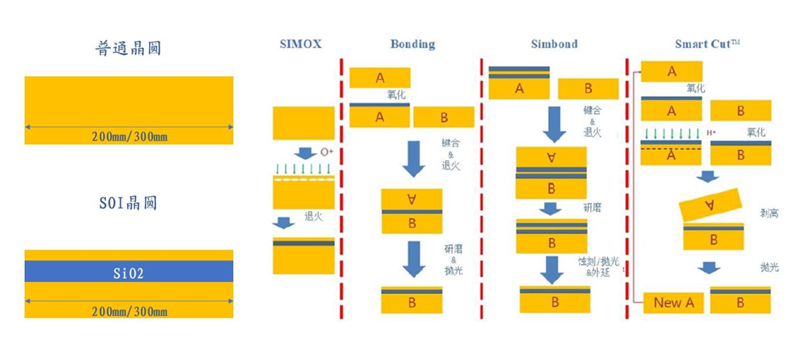

There are four main methods for manufacturing SOI silicon wafers: SIMOX technology, Bonding technology, Sim bond technology, and Smart CutTM technology; The principle of SOI silicon wafer is relatively simple, and the core goal is to add an insulating layer (usually mainly composed of silicon dioxide SiO2) in the middle of the substrate.

Four Manufacturing Technologies for SOI Silicon Wafers

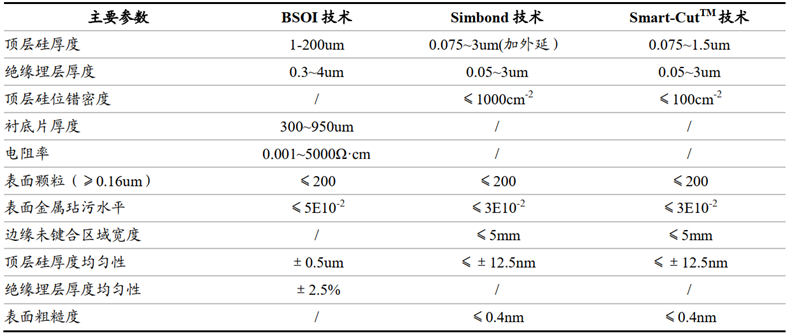

From the perspective of performance parameters, Smart CutTM technology is currently the most outstanding in SOI silicon wafer manufacturing technology. The performance of Simbond technology is not significantly different from that of Smart Cut technology, but in terms of top silicon thickness, the SOI silicon wafers produced by Smart Cut technology are thinner. Moreover, in terms of production cost, Smart Cut technology can reuse silicon wafers. For future large-scale production situations, Smart Cut technology has a cost advantage. Therefore, the industry now recognizes Smart Cut technology as the future direction for the development of SOI silicon wafers.

▲ Performance comparison of different manufacturing technologies for SOI silicon wafers

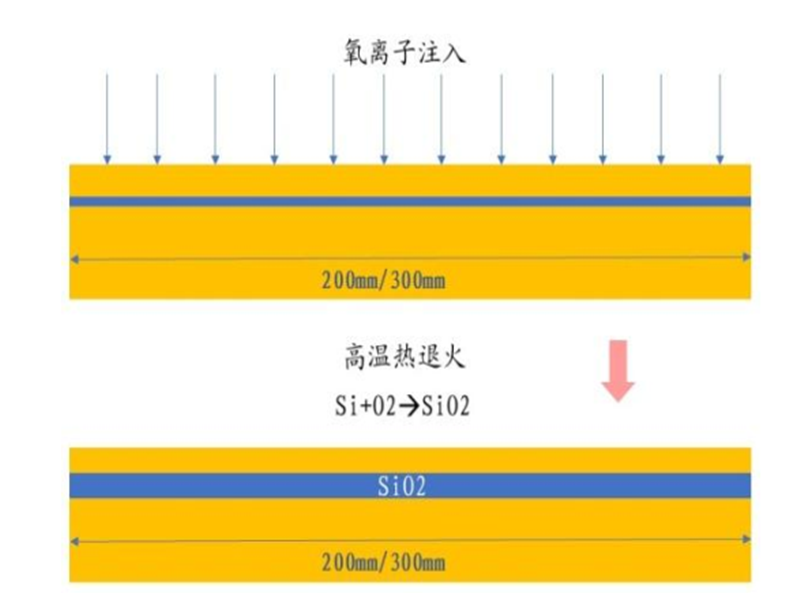

SIMOX technology: SIMOX stands for Separation by Implanted Oxygen. Injecting oxygen atoms into the wafer, followed by high-temperature annealing, causes the oxygen atoms to react with the surrounding silicon atoms, forming a layer of silicon dioxide. The difficulty of this technology is to control the depth and thickness of oxygen ion implantation. The requirements for ion implantation technology are relatively high.

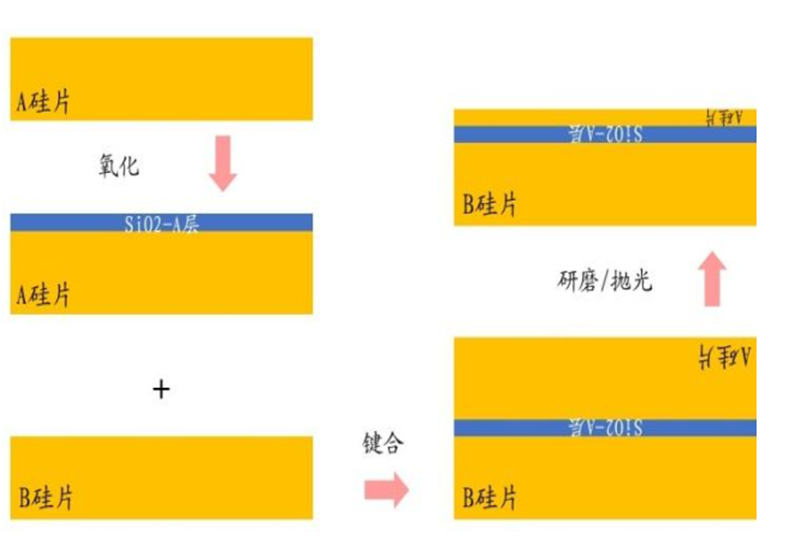

Bonding technology: Bonding technology, also known as bonding technology, is used to manufacture SOI silicon wafers, also known as bonded SOI or BSOI. Bonding technology requires two ordinary silicon wafers, on which a layer of oxide (SiO2) is grown and then bonded to the other silicon source, with the connection being the oxide layer. Finally, grind and polish to the desired depth of the buried layer (SiO2). Due to the simplicity of bonding technology compared to ion implantation technology, most SOI silicon wafers are currently produced using bonding technology.

▲ Formation of silicon on insulator by ion implantation method

▲ Wafer bonding method to form silicon on insulator

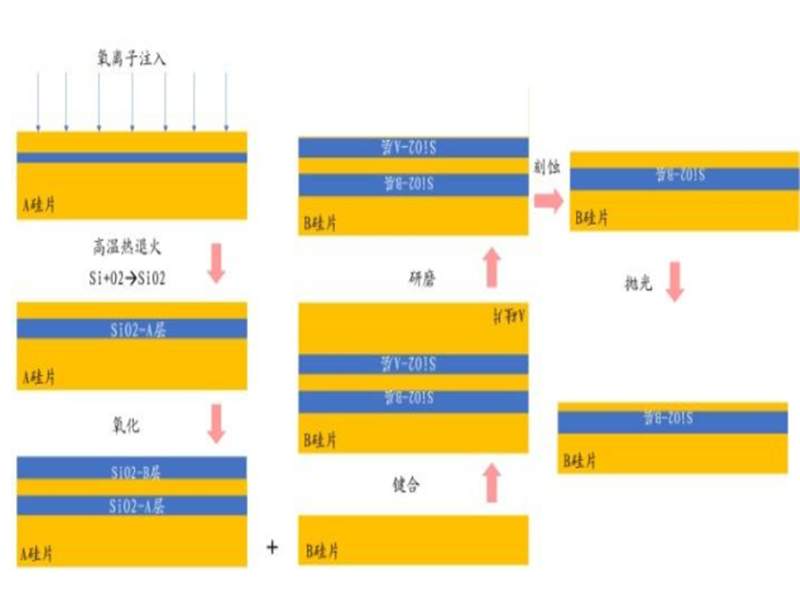

Sim bond technology: oxygen injection bonding technology. Sim bond technology is a combination of SIMOX and bond technology. The advantage is that it can accurately control the thickness of the buried oxygen layer. The first step is to inject oxygen ions into a silicon wafer, followed by high-temperature annealing to form an oxide layer, and then form a SiO2 oxide layer on the surface of the silicon wafer. The second step is to bond the silicon wafer with another wafer. Then perform high-temperature annealing to form a complete bonding interface. Step three, thinning process. Using CMP technology for thinning, but unlike bond technology, sim bond has a self stopping layer that automatically stops when polished to the SiO2 layer. Then, the SiO2 layer is removed through corrosion. The final step is polishing.

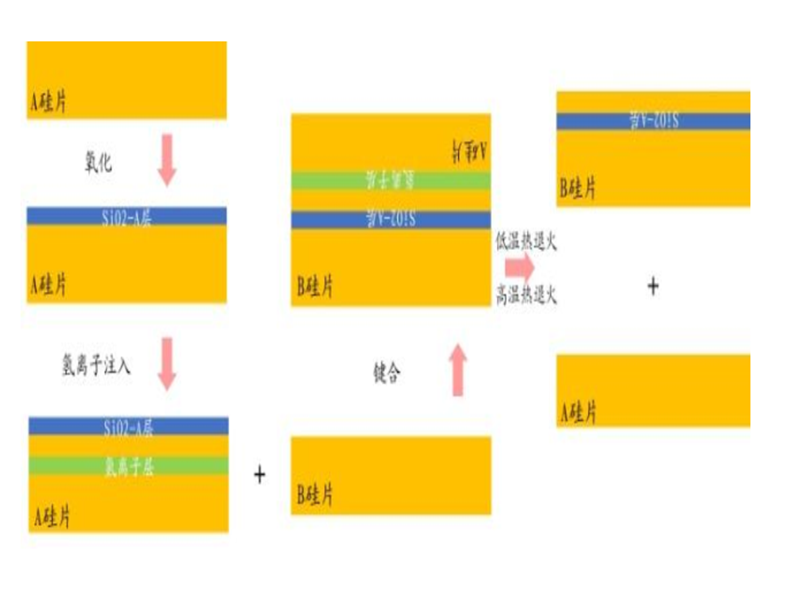

Smart cut technology: intelligent stripping technology. Smart cut technology is an extension of bonding technology. The first step is to oxidize a wafer and generate a fixed thickness of SiO2 on the wafer surface. The second step is to use ion implantation technology to inject hydrogen ions into a fixed depth of the wafer. The third step is to bond another wafer with the oxidized wafer. The fourth step is to use low-temperature annealing technology to form hydrogen ions into bubbles, causing a portion of the silicon wafer to peel off. Then, high-temperature annealing technology is used to increase the bonding strength. The fifth step is to flatten the silicon surface. This technology is internationally recognized as the development direction of SOI technology, and the thickness of the buried oxygen layer is completely determined by the depth of hydrogen ion implantation, which is more accurate. Moreover, the detached wafers can be reused, greatly reducing costs.

▲ Sim bond method for forming silicon on insulator

▲ Smart cut method for forming silicon on insulator

Advanced Institute (Shenzhen) Technology Co., Ltd, © two thousand and twenty-onewww.avanzado.cn. All rights reservedGuangdong ICP No. 2021051947-1 © two thousand and twenty-onewww.xianjinyuan.cn. All rights reservedGuangdong ICP No. 2021051947-2